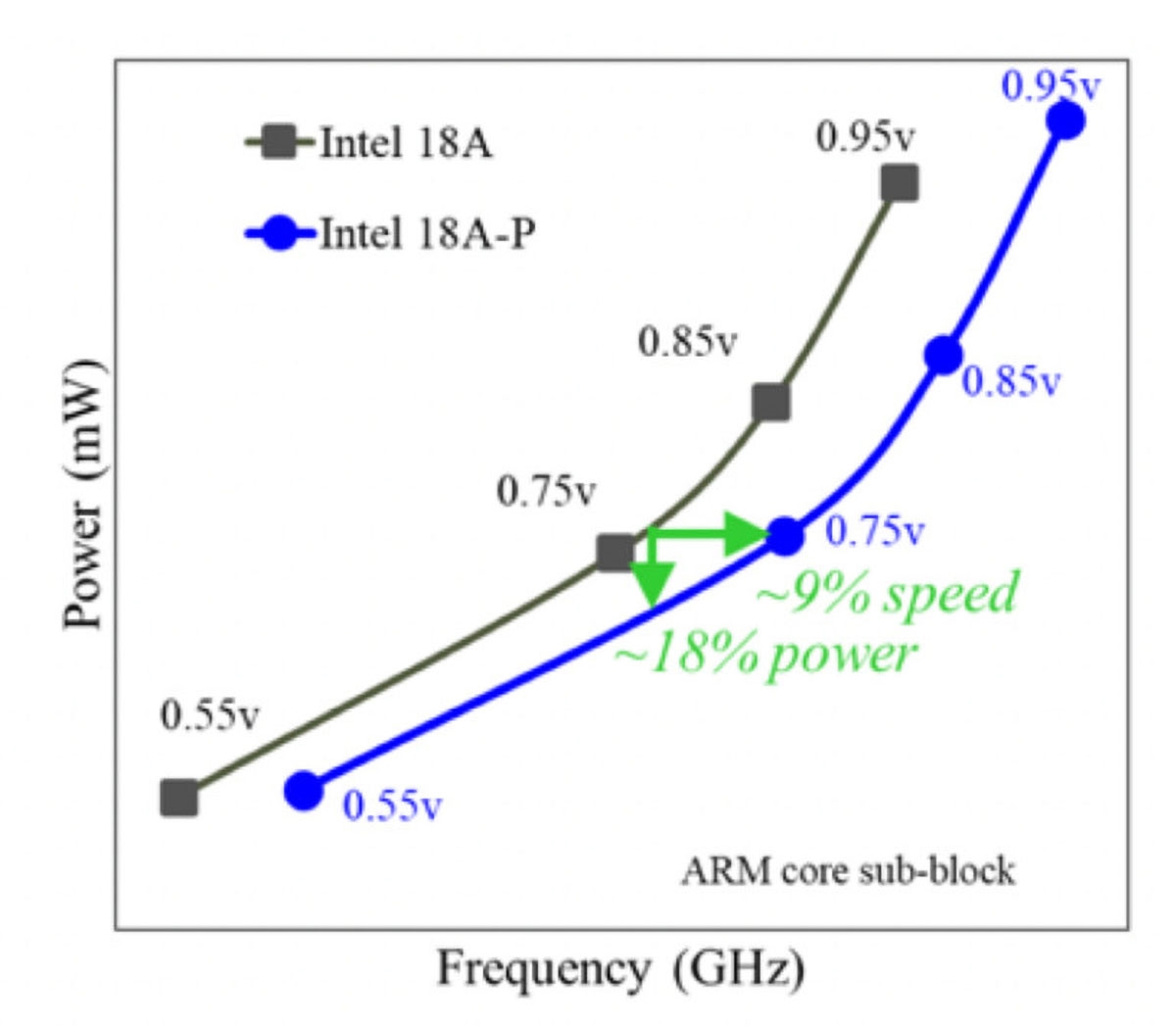

इंटेल ने होनोलूलू, हवाई में आयोजित वीएलएसआई 2026 सेमिनार में पेपर टी1.2 के माध्यम से आधिकारिक तौर पर इंटेल 18ए-पी प्रक्रिया नोड के प्रमुख तकनीकी डेटा की घोषणा की। मानक Intel 18A नोड की तुलना में, 18A-P समान बिजली खपत के तहत 9% से अधिक का प्रदर्शन लाभ प्राप्त करता है और समान प्रदर्शन के तहत बिजली की खपत को 18% से अधिक कम करता है।

इस प्रकार के प्रदर्शन और शक्ति सुधार, आमतौर पर केवल क्रॉस-जेनरेशनल नोड ट्रांज़िशन के साथ देखे जाते हैं, अब समान घनत्व पर 18A-P के साथ प्राप्त किए जा सकते हैं।

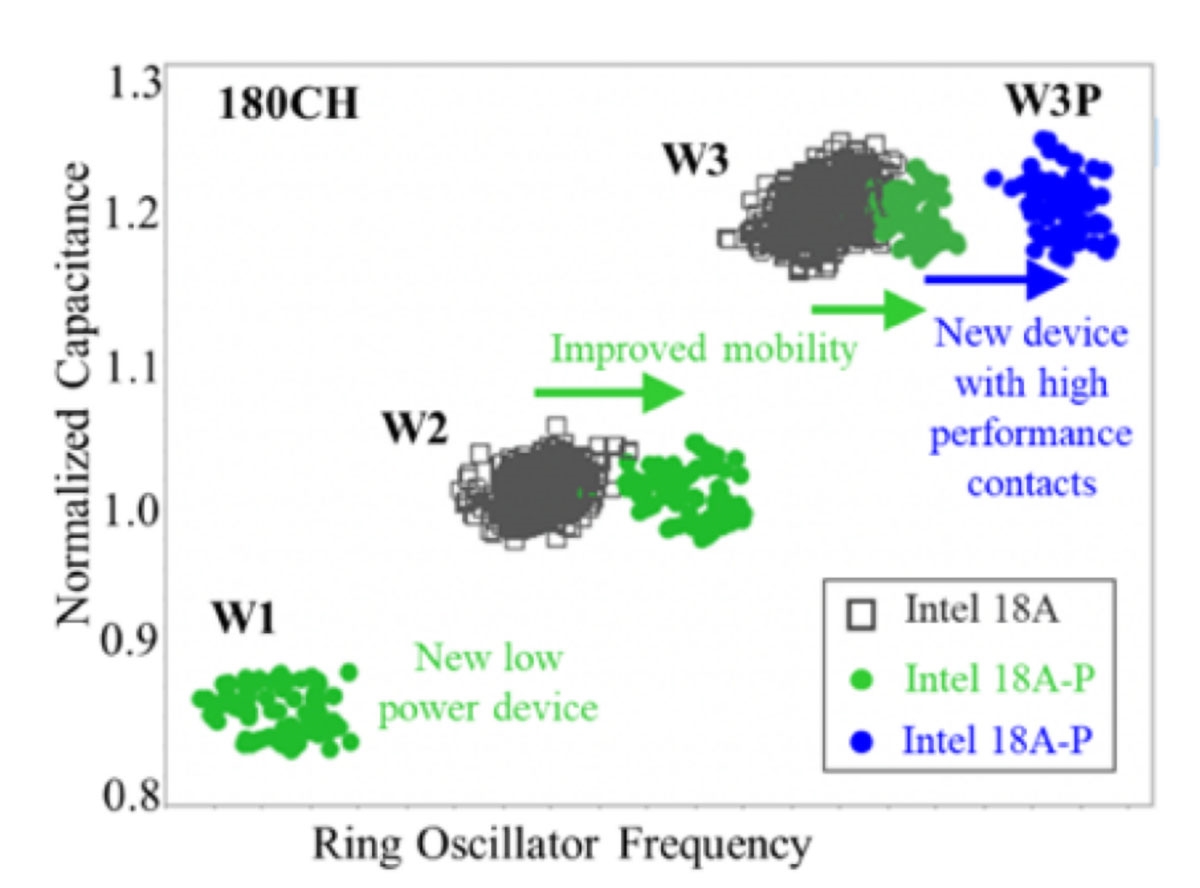

मूल इंटेल पेपर चार विशिष्ट सुधारों को सूचीबद्ध करता है: अतिरिक्त तर्क वीटी जोड़े, सख्त घड़ी ऑफसेट कोण नियंत्रण, उच्च-घनत्व (एचडी) और उच्च-प्रदर्शन (एचपी) पुस्तकालयों में नए कम-शक्ति वाले उपकरण, और दोनों पुस्तकालयों में एचपी उपकरणों के प्रदर्शन-उन्नत संस्करण।

इंटेल ने मानक 18ए की तुलना में 18ए-पी के तिरछे कोनों को लगभग 30% कम कर दिया है। एक ही वेफर पर ट्रांजिस्टर के बीच प्रदर्शन अंतर काफी कम हो जाता है, बिजली की खपत और प्रदर्शन विशेषताएँ अधिक अनुमानित होती हैं, और पैरामीटर उपज और चिप स्थिरता में एक साथ सुधार होता है।

गर्मी अपव्यय के संदर्भ में, 18A-P का थर्मल प्रतिरोध 18A की तुलना में लगभग 50% कम है, और थर्मल चालकता दक्षता में काफी सुधार हुआ है। यह उच्च-प्रदर्शन कंप्यूटिंग परिदृश्यों में निरंतर उच्च-आवृत्ति संचालन के लिए विशेष रूप से महत्वपूर्ण है, और बैक-साइड पावर सप्लाई टेक्नोलॉजी (पावरविया) द्वारा लाई गई गर्मी अपव्यय चुनौतियों का सीधे जवाब देता है।

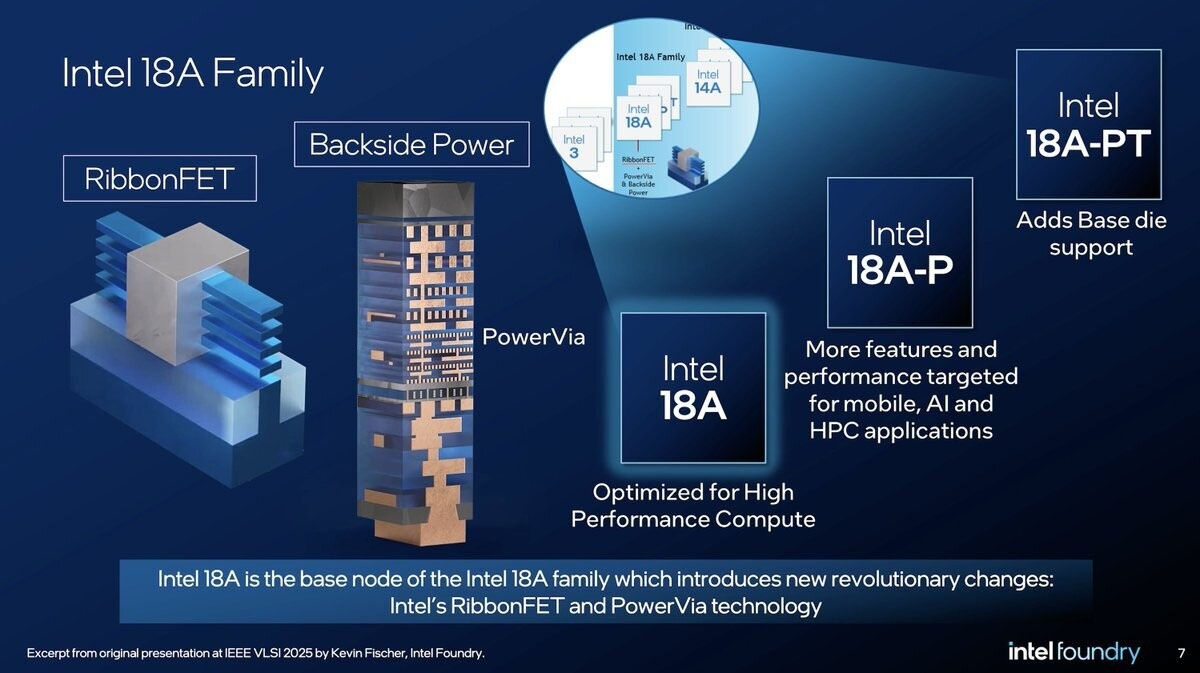

इंटेल ने संभावित ग्राहकों को 18A-P के लिए अपने PDK प्रक्रिया डिज़ाइन किट का संस्करण 1.0 भेज दिया है ताकि वे चिप सत्यापन का परीक्षण शुरू कर सकें। यह प्रक्रिया अभी भी रिबनएफईटी ऑल-अराउंड गेट ट्रांजिस्टर आर्किटेक्चर और पावरविया बैक पावर सप्लाई तकनीक पर आधारित है, और 18ए प्लेटफॉर्म का एक प्रदर्शन-उन्नत संस्करण है।

ट्रेंडफोर्स के अनुसार, ऐप्पल एम-सीरीज़ चिप्स का उत्पादन करने के लिए 18ए-पी प्रक्रिया के उपयोग का मूल्यांकन कर रहा है, जबकि Google टीपीयू वी8ई प्रोजेक्ट को बढ़ावा देने के लिए इंटेल की ईएमआईबी उन्नत पैकेजिंग तकनीक का उपयोग करने पर विचार कर रहा है। संबंधित उत्पाद 2027 की शुरुआत में लॉन्च किए जा सकते हैं।